### Sequential Circuits: Memory, Finite State Machines

Becker/Molitor, Chapter 11.3.1 Harris/Harris, Chapters 3.3, 3.4, 5.5

#### Jan Reineke Universität des Saarlandes

### Motivation: Sequential circuits

*So far*: combinatorial circuits = acyclic circuits

- Compute the same fixed Boolean function

- Not powerful enough to compute all computable functions

- → Computers process programs step-by-step:

- Fetch-decode-execute cycle

- Need memory to:

- store programs and data

- store intermediate results

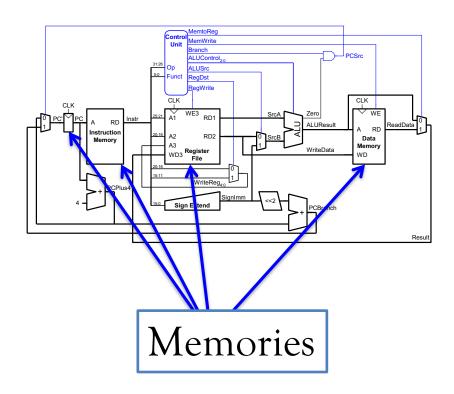

### Roadmap: Computer architecture

- 1. Combinatorial circuits: Boolean Algebra/Functions/Expressions/Synthesis

- 2. Number representations

- 3. Arithmetic Circuits: Addition, Multiplication, Division, ALU

- 4. Sequential circuits: Flip-Flops, Registers, SRAM, Moore and Mealy automata

- 5. Verilog

- 6. Instruction Set Architecture

- 7. Microarchitecture

- 8. Performance: RISC vs. CISC, Pipelining, Memory Hierarchy

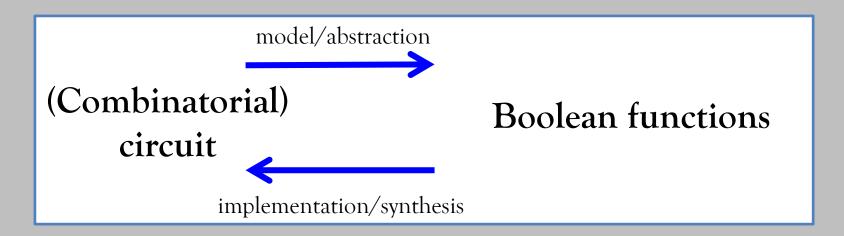

### From combinatorial to sequential circuits

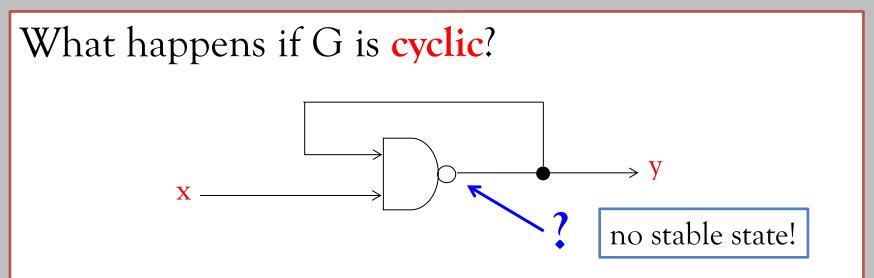

So far only combinatorial circuits:

$$C = (X_n, G, typ, IN, Y_m),$$

i.e., G was acyclic.

Circuits like this one are required to build storage elements!

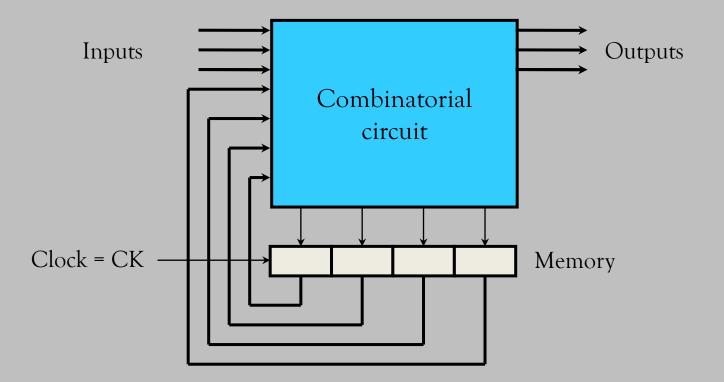

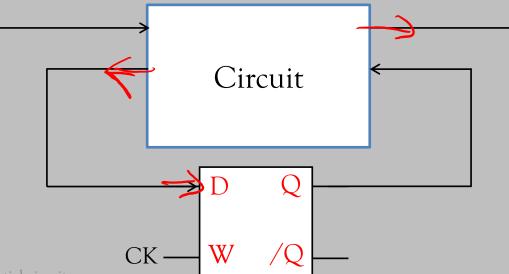

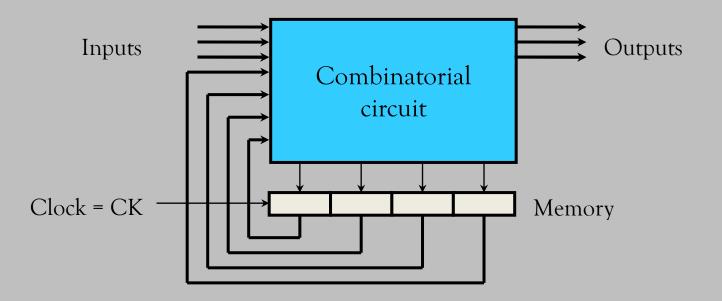

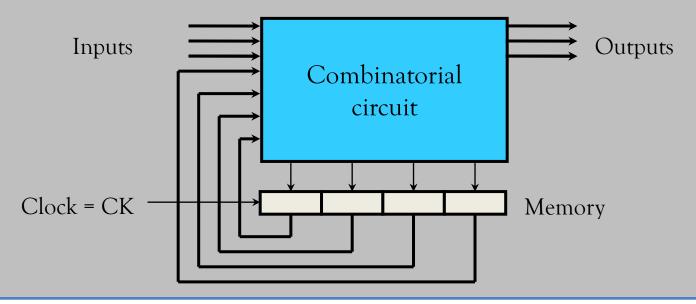

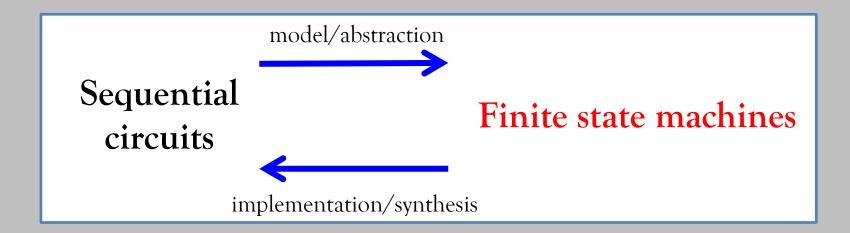

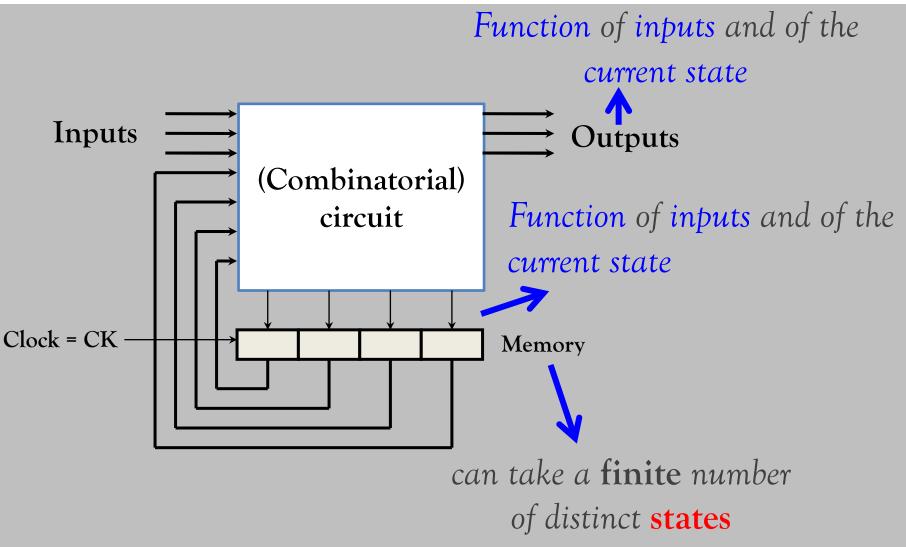

# Sequential circuits = (combinatorial) circuits + memory

Properties:

- Every cycle contains storage element

- Separation between circuits and storage elements

- Implement finite state automata (Moore or Mealy, more on these later)

### MEMORY CELLS

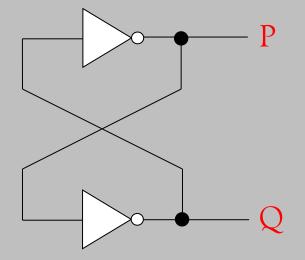

### Example: Cyclic circuit

Which values can P and Q take?

How can the values of **P** and **Q** be changed?

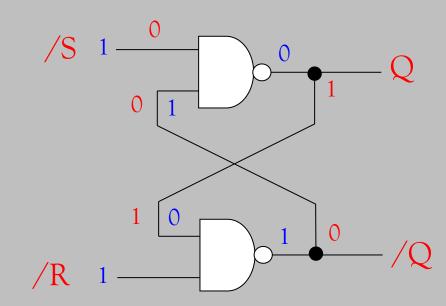

### (NAND) SR latch

*Transition*: Stable state  $Q = 0 \rightarrow$  stable state Q = 1:

"active low" terminology: /S and /R activated at low input voltage

Circuit with two stable states,

adequate to store  $\log_2 2 = 1$  bit.

At time t<sub>0</sub> lower /S and at t<sub>0</sub> + x raise it again (we call this a pulse)

2. After propagation delay  $t_{P/SQ}$  we have Q = 1.

3. After propagation delay  $t_{P/S/Q}$  we have /Q = 0.

Sequential circuits

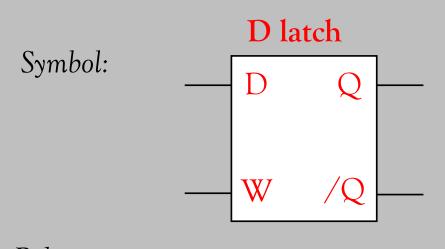

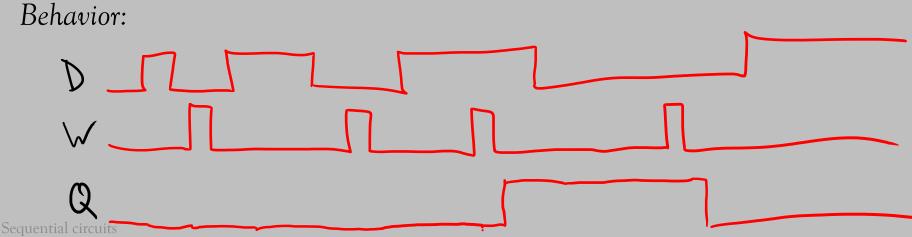

### D latch: Behavior

To store an incoming data value D via a pulse (interval between raising and lowering) at W.

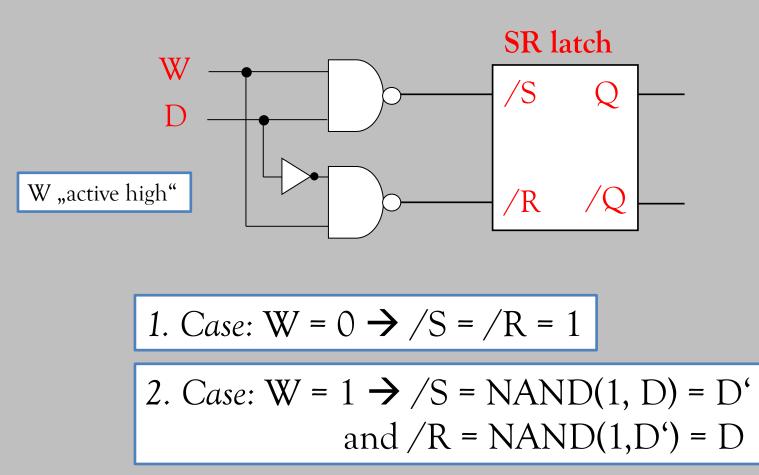

### D latch: Implementation

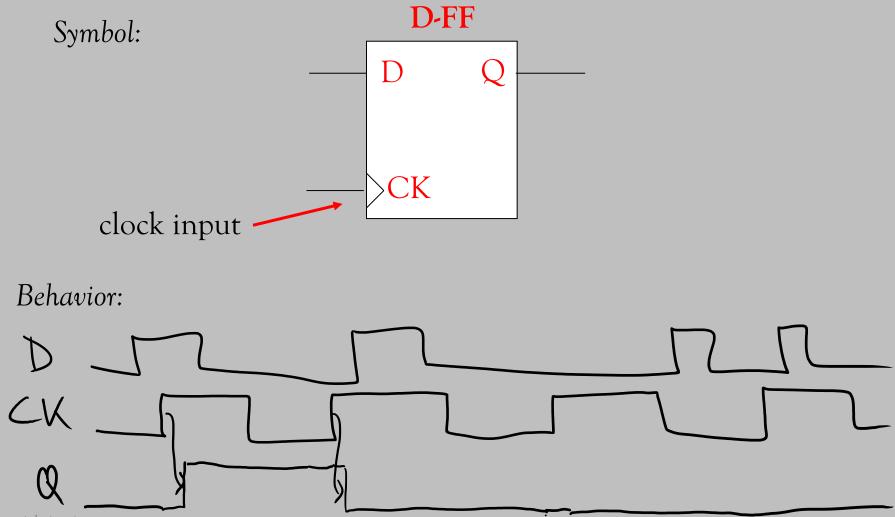

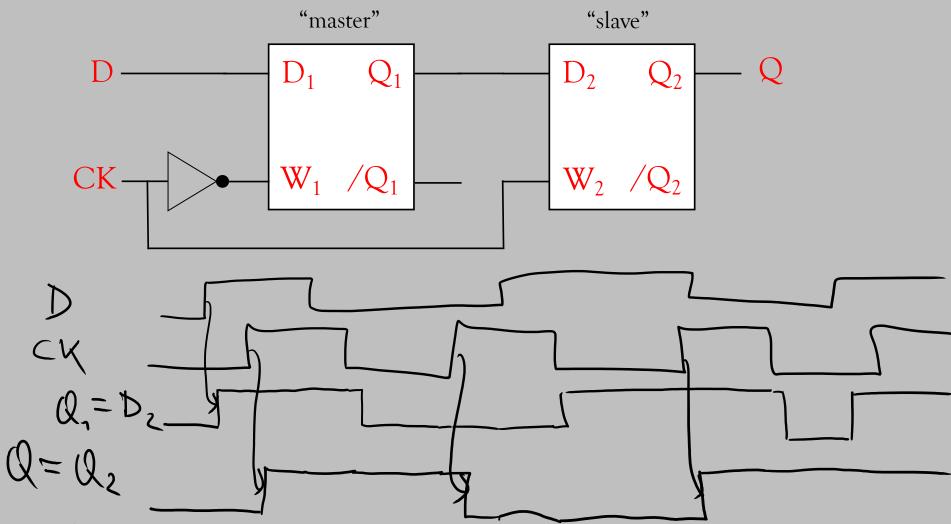

## D flip-flop: Edge-triggered

Controlled via a **rising edge** of a signal (usually of a clock):

### D flip-flop: Implementation

## Latch vs Flip-flop

- Latch = level-triggered

- Flip-flop = edge-triggered

- Advantage:

More predictable in circuits with feedback

With a **latch** the behavior depends on the precise timing of the circuit!

With a **flip-flop** the circuit just has to be "fast enough".

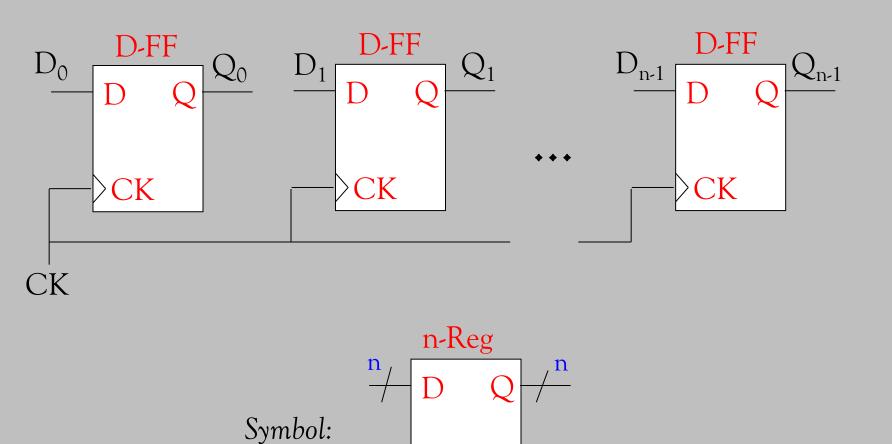

### Derived circuit: n-bit register

System Architecture, Jan Reineke

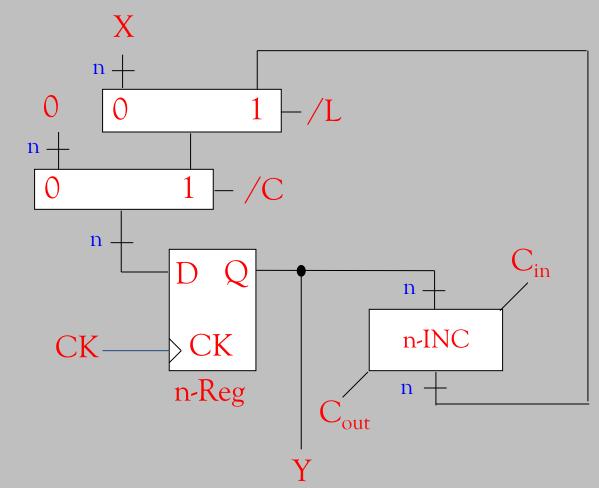

### A simple sequential circuit: An n-bit counter

/C clear, /L load, X input, Y output

### STATIC RAM AND DYNAMIC RAM

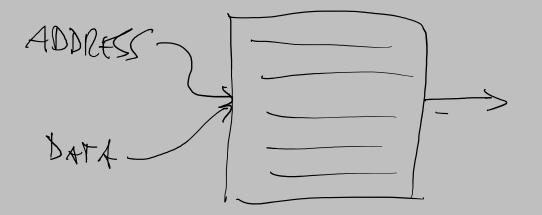

### Derived circuit: Random access memory (RAM)

Characteristics:

- linear array of storage cells

- single storage cell selected by adress

- Reading and writing possible

- **volatile =** not persistent = loses its state if power is off.

### Schematic of an SRAM (a single addressed bit)

### Decoder

#### Definition:

An **n-bit decoder** is a circuit that computes the following Boolean function  $f : B^n \rightarrow B^N$ , with N = 2<sup>n</sup>:

$$y_{i} = f(x_{n-1}...x_{0})_{i} \Leftrightarrow \left(\left\langle x_{n-1}...x_{0}\right\rangle = i\right)$$

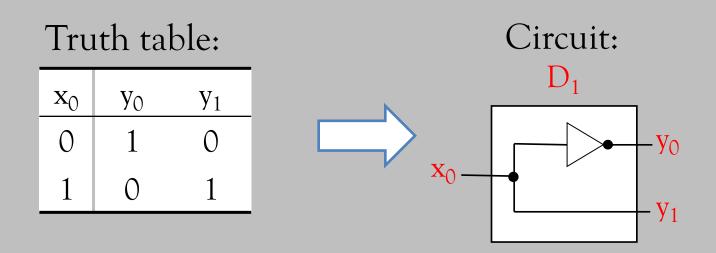

### Base case: 1-bit decoder

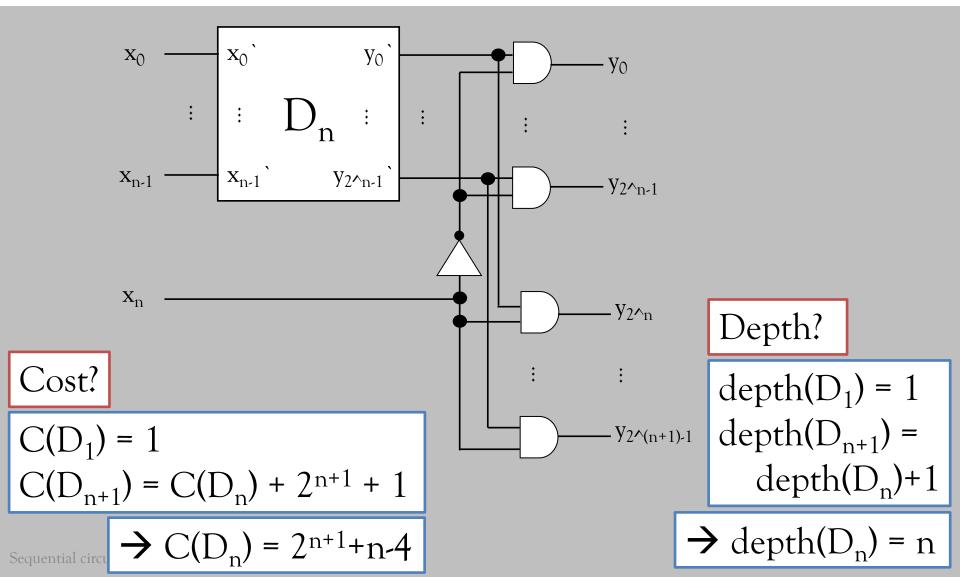

#### Properties:

- 1 input,  $2^1 = 2$  outputs

- Depth: depth $(D_1) = 1$

- Cost:  $C(D_1) = 1$

# n-Bit decoder: Recursive construction (from $D_n$ to $D_{n+1}$ )

### Correctness of an n-bit decoder

- Proof by induction over *n*:

- Base case (n=1):  $\checkmark$

- Induction step (n  $\rightarrow$  n+1):

- Need to show for all  $0 \le i \le 2^{n+1}$ :

- Case distinction:

$$y_i \Longleftrightarrow \left( \left\langle x_n x_{n-1} \dots x_0 \right\rangle = i \right)$$

1.  $0 \le i \le 2^n$ : by construction we have:

$$y_{i} \Leftrightarrow y'_{i} \wedge \overline{x}_{n} \stackrel{\text{I.H.}}{\Leftrightarrow} \left( \left\langle x_{n-1} \dots x_{0} \right\rangle = i \right) \wedge \overline{x}_{n} \Leftrightarrow \left( \left\langle x_{n} x_{n-1} \dots x_{0} \right\rangle = i \right)$$

2.  $2^n \le i \le 2^{n+1}$ : by construction we have:

$$y_{i-2^{n}} \Leftrightarrow y'_{i-2^{n}} \land x_{n} \stackrel{\text{I.H.}}{\Leftrightarrow} \left( \left\langle x_{n-1} \dots x_{0} \right\rangle = i - 2^{n} \right) \land x_{n} \Leftrightarrow \left( \left\langle x_{n} x_{n-1} \dots x_{0} \right\rangle = i \right)_{22}$$

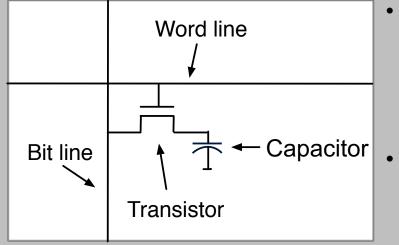

### Alternative: Dynamic RAM (DRAM)

- Word line active, when bit is read or written to, transistor transmits

- Writing:

- Voltage on **bit line**

- high for 1, low for 0

- Pulse on word line

- transfers charge to capacitor

- Reading:

- Charge of capacitor is transferred via the bit line to a sense amplifier

- compares with reference value to detect 0 or 1

- Capacitor "leaks" charge.

State must be refreshed periodically; according to standard every 64 ms → thus "dynamic" RAM

- temperature-dependent

- less leakage the colder the transistor is

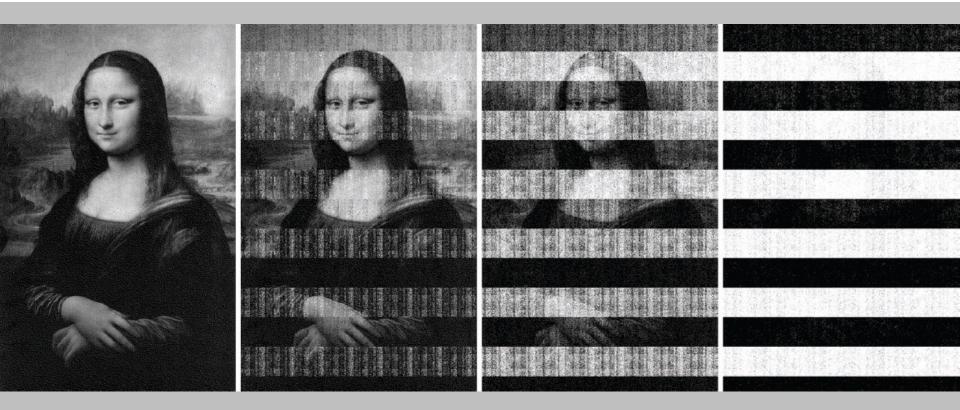

### Anecdote: "Memory attacks"

#### Lest We Remember: Cold-Boot Attacks on Encryption Keys Communications of the ACM, 2009

Sequential circuits

### Comparison: SRAM vs DRAM

### Both are volatile:

i.e. must expend energy to keep data

| Static RAM                                                 | Dynamic RAM                                                          |

|------------------------------------------------------------|----------------------------------------------------------------------|

| requires 6 transistors per bit $\rightarrow$ lower density | requires 1 transistor and<br>1 capacitor per bit<br>→ higher density |

| faster accesses                                            | slower accesses                                                      |

|                                                            | requires refresh                                                     |

| $\rightarrow$ used in caches                               | $\rightarrow$ used in main memory                                    |

### SEQUENTIAL CIRCUITS

Sequential circuits

System Architecture, Jan Reineke

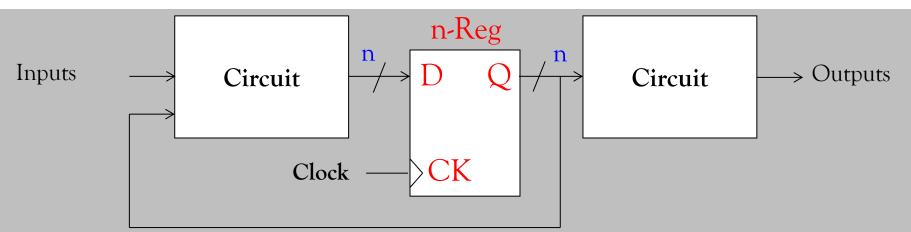

# Sequential circuits = (combinatorial) circuits + memory

Properties:

- Every cycle contains storage element

- Separation between circuits and storage elements

# Sequential circuits = (combinatorial) circuits + memory

Wanted:

- Predictable, deterministic behavior:

- deterministic: same output sequence on same input sequence

- predictable: can mathematically capture input/output behavior

Required for that:

• Depth of combinatorial circuit < length of a clock cycle

### FINITE STATE MACHINES

Sequential circuits

System Architecture, Jan Reineke

# Finite state machines as models of sequential circuits

### Sequential circuits: Abstraction

### Finite state machine, Mealy machine

Definition:

A Mealy machine is a 6-tuple  $M=(Q, q_0, I, O, \delta, \lambda)$ :

- Q is a finite, non-empty set of states,

- $q_0 \in Q$  is the initial state,

- I is a *finite*, *non-empty* input alphabet,

- O is a *finite*, *non-empty* output alphabet,

- $\delta : Q \ge I \rightarrow Q$  is the transition function,

- $\lambda : Q \ge I \rightarrow O$  is the output function.

Named after: Mealy, George H. (1955), "A method for synthesizing sequential circuits", Bell System Technical Journal

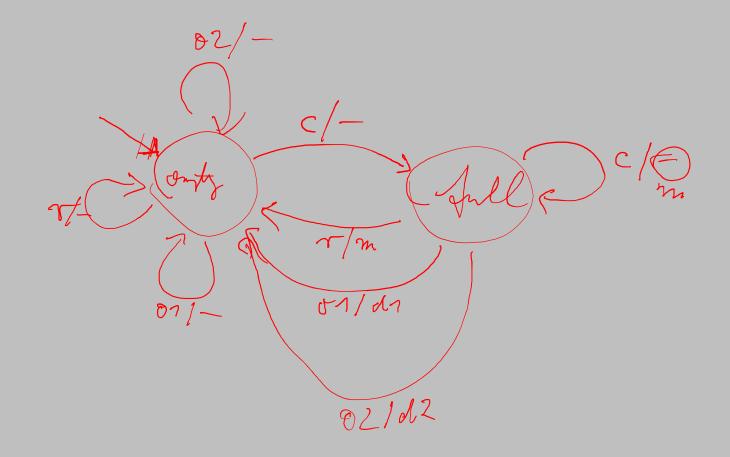

### Mealy machine: Example vending machine

- A (simple) vending machine:

1. Pay one euro,

2a. Then choose one among two drinks.

- 2b. Or press the return button to retrieve the money

- Other behavior is ignored by the vending machine.

### Example: Vending machine

- Set of states Q?

- Input alphabet I?

- Output alphabet O?

- $Q = \{empty, full\}, q_0 = empty$

- I = {coin (c), return (r), option 1 (o1), option 2 (o2)}

- O = {no output (-), emission of money (m), emission of drink 1 (d1), emission of drink 2 (d2)}

### *Example*: Vending machine Transition and output function graphically

## *Example*: Vending machine Transition and output function

#### Transition function:

| Q     | Ι  | δ     |

|-------|----|-------|

| empty | С  | full  |

| empty | r  | empty |

| empty | 01 | empty |

| empty | 02 | empty |

| full  | С  | full  |

| full  | r  | empty |

| full  | 01 | empty |

| full  | 02 | empty |

#### Output function:

| Q     | Ι  | λ  |

|-------|----|----|

| empty | С  | -  |

| empty | r  | -  |

| empty | d1 | -  |

| empty | d2 | -  |

| full  | С  | -  |

| full  | r  | m  |

| full  | d1 | 01 |

| full  | d2 | 02 |

## From Mealy machines to Sequential circuits

How can we turn transition and output functions into Boolean functions?

## From Mealy machines to Sequential circuits

- 1. Fix encoding of states, inputs, and outputs

- 2. Synthesize **circuits** for *transition function* and *output function*

### Example: Vending machine 1. Encoding

- 2 states, i.e., we require at least one bit.

Assume *empty* → 0, *full* → 1.

- 4 inputs and 4 outputs, and so we require at least 2 bits, as  $4 = 2^2$ .

#### For example:

| Ι  | <b>X</b> 1 | X2 | 0  | <b>Y</b> 1 | <b>Y</b> 2 |

|----|------------|----|----|------------|------------|

| С  | 0          | 0  | -  | 0          | 0          |

| r  | 0          | 1  | m  | 0          | 1          |

| 01 | 1          | 0  | d1 | 1          | 0          |

| 02 | 1          | 1  | d2 | 1          | 1          |

Truth table of transition function follows from encoding:

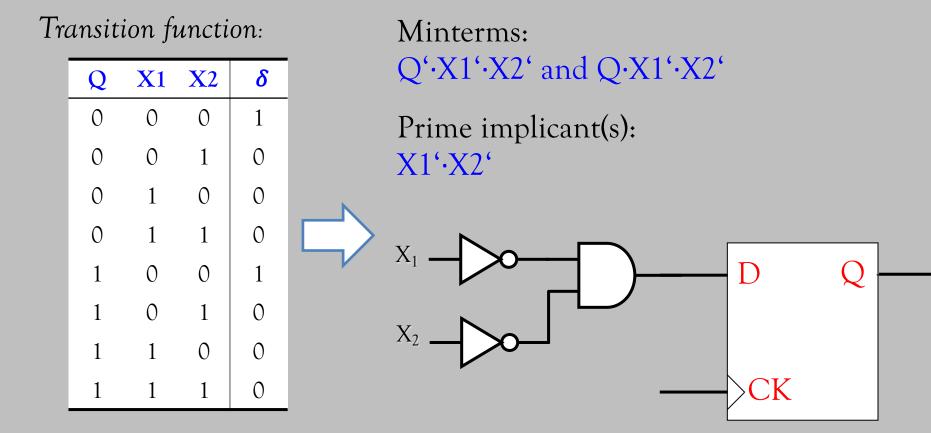

#### Transition function:

| Q     | I  | δ     | Q | <b>X</b> 1 | <b>X</b> 2 | δ |

|-------|----|-------|---|------------|------------|---|

| empty | С  | full  | 0 | 0          | 0          | 1 |

| empty | r  | empty | 0 | 0          | 1          | 0 |

| empty | 01 | empty | 0 | 1          | 0          | 0 |

| empty | 02 | empty | 0 | 1          | 1          | 0 |

| full  | С  | full  | 1 | 0          | 0          | 1 |

| full  | r  | empty | 1 | 0          | 1          | 0 |

| full  | 01 | empty | 1 | 1          | 0          | 0 |

| full  | 02 | empty | 1 | 1          | 1          | 0 |

#### Synthesis of a circuit for the transition function:

Truth table of output function follows from encoding:

#### Output function:

| Q     | Ι  | λ  |   | Q | <b>X</b> 1 | X2 | <b>Y1</b> | <b>Y</b> 2 |

|-------|----|----|---|---|------------|----|-----------|------------|

| empty | С  | -  |   | 0 | 0          | 0  | 0         | 0          |

| empty | r  | -  |   | 0 | 0          | 1  | 0         | 0          |

| empty | 01 | -  | Ν | 0 | 1          | 0  | 0         | 0          |

| empty | 02 | -  |   | 0 | 1          | 1  | 0         | 0          |

| full  | С  | -  | V | 1 | 0          | 0  | 0         | 0          |

| full  | r  | m  |   | 1 | 0          | 1  | 0         | 1          |

| full  | 01 | d1 |   | 1 | 1          | 0  | 1         | 0          |

| full  | 02 | d2 |   | 1 | 1          | 1  | 1         | 1          |

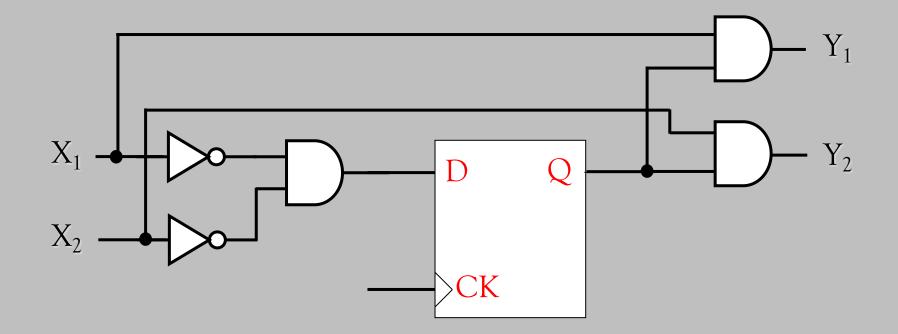

### Synthesis of a circuit for the output function:

Output function:

| Ε | Q | <b>X</b> 1 | <b>X</b> 2 | <b>Y1</b> | <b>Y2</b> |  |

|---|---|------------|------------|-----------|-----------|--|

| Γ | 0 | 0          | 0          | 0         | 0         |  |

|   | 0 | 0          | 1          | 0         | 0         |  |

|   | 0 | 1          | 0          | 0         | 0         |  |

|   | 0 | 1          | 1          | 0         | 0         |  |

|   | 1 | 0          | 0          | 0         | 0         |  |

|   | 1 | 0          | 1          | 0         | 1         |  |

|   | 1 | 1          | 0          | 1         | 0         |  |

|   | 1 | 1          | 1          | 1         | 1         |  |

Minterms for Y1: Q·X1·X2' and Q·X1·X2

Prime implicant(s): Q·X1

Minterms for Y2: Q·X1<sup>·</sup>·X2 and Q·X1·X2

Prime implicant(s): Q·X2

# *Example*: Vending machine Sequential circuit

## From Mealy machines to Sequential circuits

Encoding may strongly influence cost and depth of resulting circuits!

For lack of time we do not further consider this topic in this course.

## Alternative: Moore machine

Definition:

- A Moore machine is a tuple  $M=(Q, q_0, I, O, \delta, \lambda)$ :

- Q is a finite, non-empty set of states,

- $q_0 \in Q$  is the initial state,

- I is a *finite*, *non-empty* input alphabet,

- O is a *finite*, *non-empty* output alphabet,

- $\delta : Q \ge I \rightarrow Q$  is the transition function,

- $\lambda : Q \rightarrow O$  is the output function.

Named after: Moore, Edward F. (1956), "Gedanken-experiments on Sequential Machines", Automata Studies

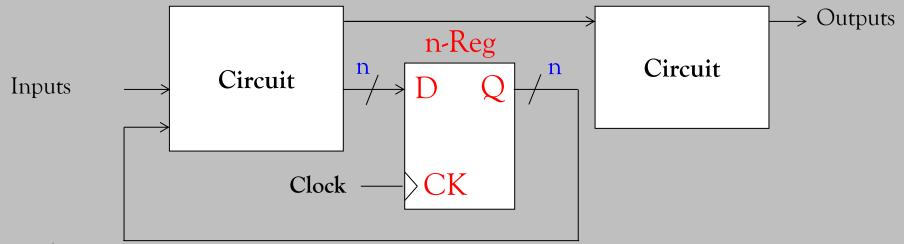

## From Moore machines to Sequential circuits

#### In contrast to Mealy automata:

Sequential circuits

## Moore- vs Mealy machines

- Mealy machines *react faster* on inputs: reaction in the same cycle

- Mealy machines often require *fewer states*: Need not store current input

- Moore machines can be more "safely" composed:

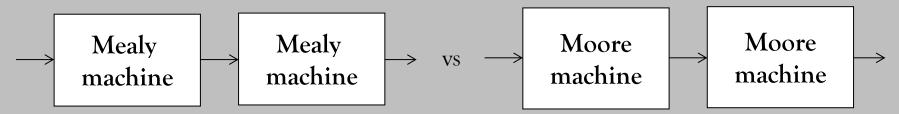

"Serial composition":

## Moore- vs Mealy machines

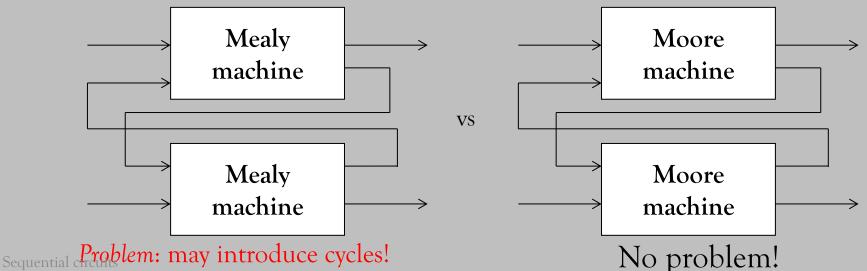

- Mealy machines *react faster* on inputs: reaction in the same cycle

- Mealy automata often require *fewer states*: Need not store current input

- Moore automata can be more *"safely"* composed: *"Feedback composition"*:

## Summary

- Cyclic circuits are necessary to implement storage elements:

- **Latches** are level-triggered

- Flip-flops are edge-triggered

- Memory technologies:

- **SRAM**: fast, but low density

- **DRAM**: slower, but higher density

- Mathematical models for sequential circuits:

- Mealy machine:

- Output depends on current state and current input

- Moore machine: Output depends only on current state