#### Multi-level Logic: Combinatorial Circuits

Becker/Molitor, Chapter 8.1

#### Jan Reineke Universität des Saarlandes

#### Implementation of Boolean functions

Wanted:

- Cheaper representations that need not be based on Boolean polynomials

- There are Boolean functions whose best representations via Boolean polynomials are very expensive...

- Practical implementation of these representations

Approach:

- Find implementations for simple Boolean functions

- Compose these to implement more complex functions

→ leads to hierarchical models

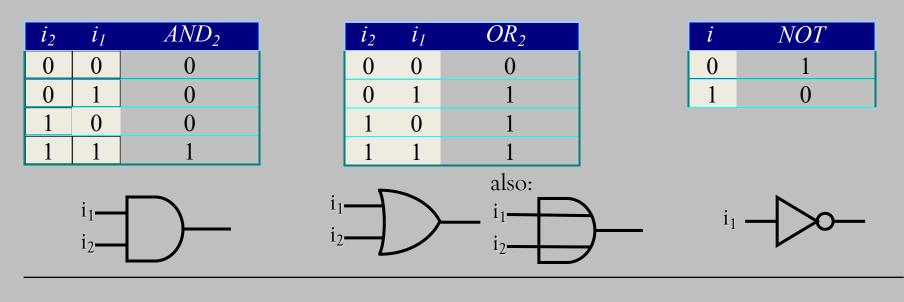

#### Examples of simple Boolean functions...

| <i>i</i> <sub>2</sub> | $i_{I}$ | $NAND_2$ |

|-----------------------|---------|----------|

| 0                     | 0       | 1        |

| 0                     | 1       | 1        |

| 1                     | 0       | 1        |

| 1                     | 1       | 0        |

| <i>i</i> <sub>2</sub> | <i>i</i> 1 | $NOR_2$ |

|-----------------------|------------|---------|

| 0                     | 0          | 1       |

| 0                     | 1          | 0       |

| 1                     | 0          | 0       |

| 1                     | 1          | 0       |

| <i>i</i> <sub>2</sub> | $i_1$ | $XOR_2$ |

|-----------------------|-------|---------|

| 0                     | 0     | 0       |

| 0                     | 1     | 1       |

| 1                     | 0     | 1       |

| 1                     | 1     | 0       |

Circuits

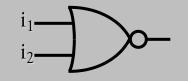

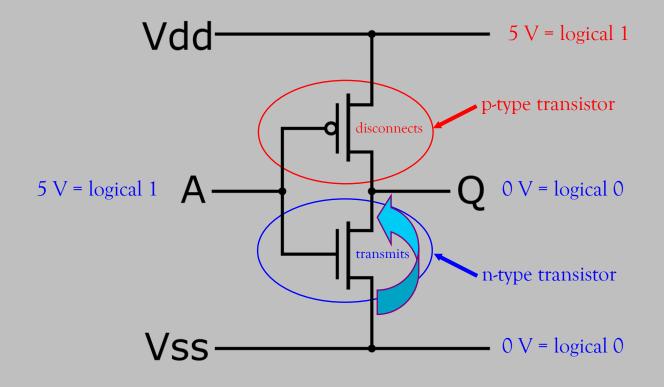

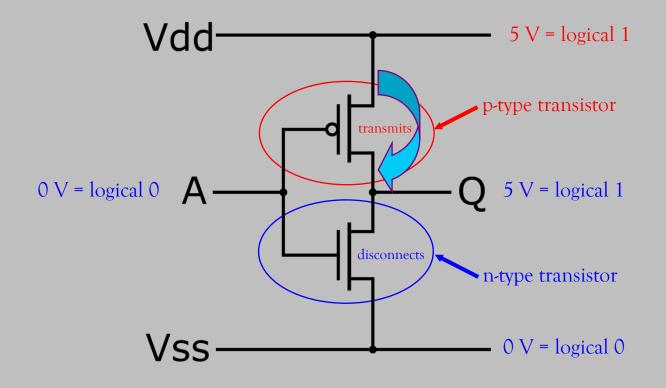

#### Short excursion: Transistors

- A transistor can be seen as a voltage-controlled switch:

- Gate g controls the conductivity between source and sink

- n-type transistor:

- transmits, if gate is 1

- disconnects, if gate is 0

- p-type transistor:

- transmits, if gate is 0

- disconnects, if gate is 1

#### Short excursion: MOS transistors

- CMOS = Complementary Metal Oxide Semiconductor

- CMOS uses n-type as well as "complementary" p-type transistors

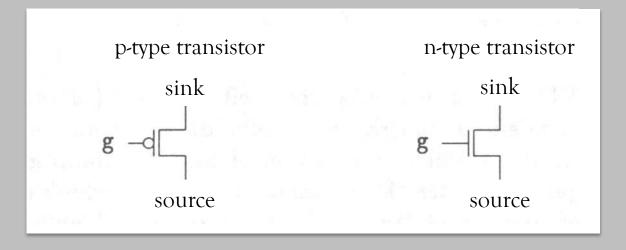

### Short excursion: CMOS inverter (1/3)

### Short excursion: CMOS inverter (2/3)

#### Short excursion: CMOS inverter (3/3)

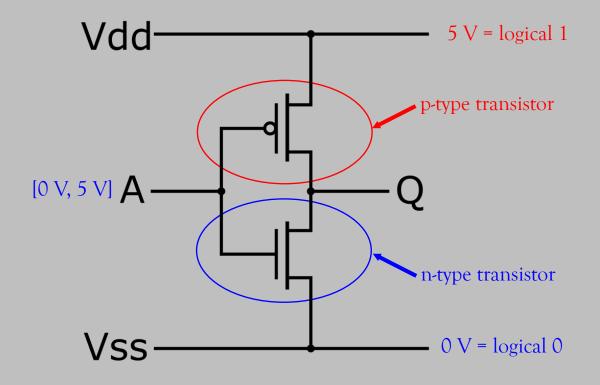

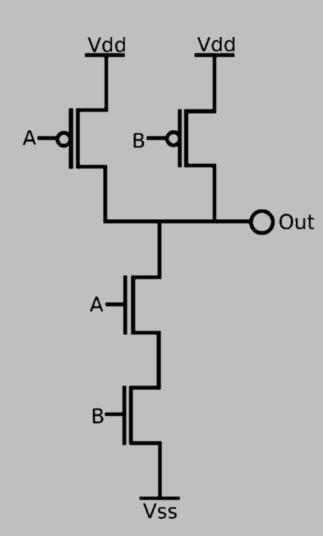

## Short excursion: CMOS NAND

Output is 0 *iff* there is a transmitting path from 0 to the output, i.e., *iff* both n-type transistors transmit, a = b = 1, then NAND(a, b) = 0

Output is 1 iff

there is a transmitting path from 1 to the output, i.e., *iff* **one** of the p-type transistors transmits, a = 0 or b = 0, then NAND(a, b) = 1

#### Implementation of Boolean functions

• In this way, implementations of all required **basic operations** are designed.

These comprise the cells of a **cell library**.

More complex functions:

"Composition" of these basic operations

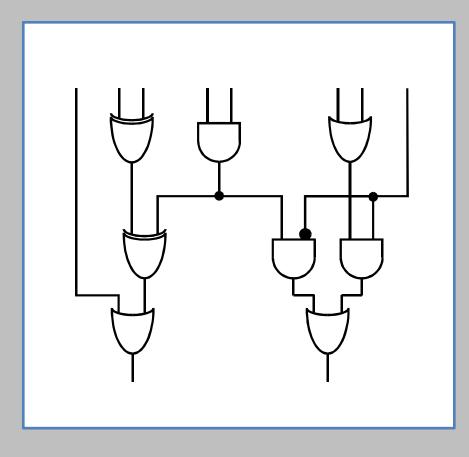

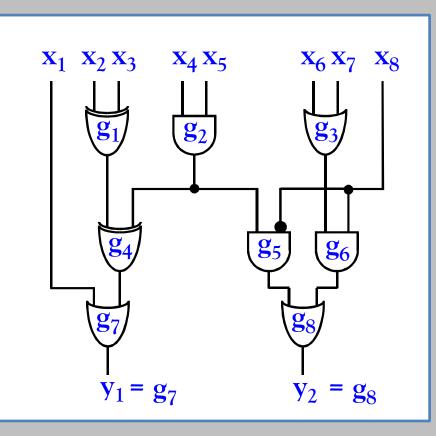

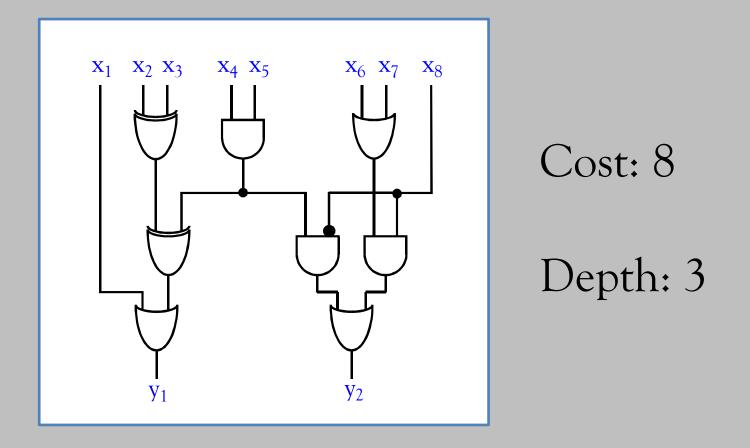

#### Implementation of Boolean functions: Example of a Boolean function $f \in \mathbf{B}_{8, 2}$

#### Questions:

- 1. How to model circuits mathematically?

- 2. Which Boolean function is computed by a given circuit?

- Concrete simulation

- Symbolic simulation

Syntax

Semantics

## Modeling circuits

Intuitively:

A **circuit** is a **directed graph** with some additional properties.

## Modeling circuits (1/3)

- A cell library  $BIB \subseteq B_n$  contains basic operations corresponding to basic gates

- A 5-tuple C =  $(X_n, G, type, IN, Y_m)$  is called **circuit** with **n** inputs and **m** outputs (for library BIB) *iff*

$-X_n = (x_1, ..., x_n)$  is a finite sequence of inputs.

- G = (V, E) is a directed acyclic graph (DAG) with {0, 1}  $\cup$  {x<sub>1</sub>, ..., x<sub>n</sub>}  $\subseteq$  V and E  $\subseteq$  V x V.

- The set  $I = V \setminus (\{0, 1\} \cup (x_1, ..., x_n))$  is called the set of gates.

## Modeling circuits (2/3)

- The mapping type :  $I \rightarrow BIB$  assigns a cell type type(v)  $\in BIB$  to each gate  $v \in I$ .

- For each gate  $v \in I$  with  $type(v) \in \mathbf{B}_k$ we have indeg(v) = k. For  $v \in V \setminus I = \{0, 1\} \cup \{x_1, ..., x_n\}$  we have indeg(v) = 0.

## Modeling circuits (3/3)

- The mapping IN : I → V\* determines the order of the incoming edges, i.e., if indeg(v) = k then IN(v) = (v<sub>1</sub>, ..., v<sub>k</sub>) with ∀1≤i≤k: (v<sub>i</sub>, v) ∈ E.

- The sequence  $Y_n = (y_1, ..., y_n)$  designates the nodes  $y_i \in V$  as the circuit's outputs.

#### Example circuit

Types of gates:  $type(g_1) = type(g_4) = XOR_2$  $type(g_2) = type(g_6) = AND_2 \dots$

Inputs:  $\chi = (x_1, x_2, x_3, x_4, x_5, x_6, x_7, x_8)$ Outputs:  $Y = (g_7, g_8)$ Gates:  $I = \{g_1, g_2, g_3, g_4, g_5, g_6, g_7, g_8\}$ Edges of the graph:  $E = \{(x_1, g_7), (x_2, g_1), (x_3, g_1), (x_4, g_2)\}$  $(x_5,g_2), (x_6,g_3), (x_7,g_3), (x_8,g_5),$  $(x_8,g_6), (g_1,g_4), (g_2,g_4), \ldots \}$

Order of the incoming edges:  $IN(g_1)=(x_2, x_3)$  $IN(g_4)=(g_1, g_2) \dots$

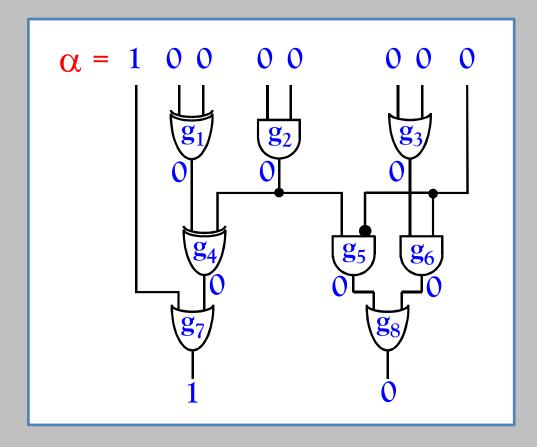

## Semantics of circuits (1/2)

- Let  $C = (X_n, G, typ, IN, Y_m)$  be a circuit for the cell library BIB.

- Let  $\alpha = (\alpha_1, ..., \alpha_n) \in \mathbf{B}^n$  be an **input valuation**.

- A valuation  $\Phi_{C,\alpha}: V \to \{0, 1\}$  for all nodes  $v \in V$  is given via the following definitions:

$$-\Phi_{\mathrm{C},\alpha}(x_i) = \alpha_i \forall 1 \le i \le n$$

$$-\Phi_{C,\alpha}(0) = 0, \Phi_{C,\alpha}(1) = 1$$

- If  $v \in I$  with

$type(v) = g \in \mathbf{B}_k \text{ and } IN(v) = (v_1, ..., v_k),$

then

$\Phi_{\mathrm{C},\alpha}(v) := \mathrm{g}(\Phi_{\mathrm{C},\alpha}(v_1), ..., \Phi_{\mathrm{C},\alpha}(v_k)).$

Why is  $\Phi_{C,\alpha}(v)$  well-defined?

Because the underlying graph G is **acyclic**!

## Semantics of circuits (2/2)

- Then  $(\Phi_{C,\alpha}(y_1), ..., \Phi_{C,\alpha}(y_m))$  is the **output valuation** of the circuit under the **input valuation**  $\alpha = (\alpha_1, ..., \alpha_n)$ .

- The computation of  $\Phi_{C,\alpha}$  under the input valuation  $\alpha$  is called **simulation** of C under valuation  $\alpha$ .

#### Example: Simulation

# Which Boolean function does a circuit compute?

Definition: The function computed at a node v  $\psi(v): B^n \to B$ is defined as  $\psi(v)(\alpha) := \Phi_{C,\alpha}(v)$ for an arbitrary  $\alpha \in B_n$ .

#### **Definition:**

The function computed by circuit C is  $f_C := (\psi(y_1), ..., \psi(y_m))$

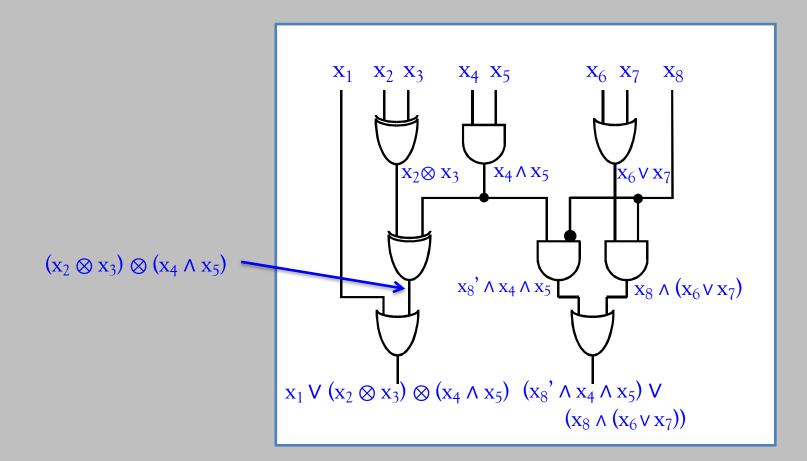

## Symbolic simulation

- Symbolic simulation does not simulate a circuit for fixed Boolean inputs. Rather it simulates the circuit on Boolean variables.

- In this way it determines the **Boolean expression** representing the **Boolean function** computed by a circuit

#### Example: Symbolic simulation

#### Brainstorming: Cost and Speed

What are reasonable measures of (a) Cost and (b) Speed of circuits?

#### Cost of circuits

Definition (Cost):

The hardware cost C(C) of a circuit C is its number of gates  $|I| = |V \setminus (\{0, 1\} \cup (x_1, ..., x_n))|$ .

#### Remark:

- Circuits are defined based on a cell library BIB

→ Cost depends on the choice of the library.

- If not stated otherwise, in the following we will use the standard library STD:

STD := {NOT, AND, OR, EXOR, NAND, NOR}

## Speed of a circuit

Definition (Depth):

The depth depth(C) of a circuit C is the maximal number of gates on a path from an arbitrary input  $x_i$  to an arbitrary output  $y_i$  of C.

#### Remark:

• Depth is only a reasonable indicators of a circuit's speed if the switching speed of each gate in the library is approximately the same.

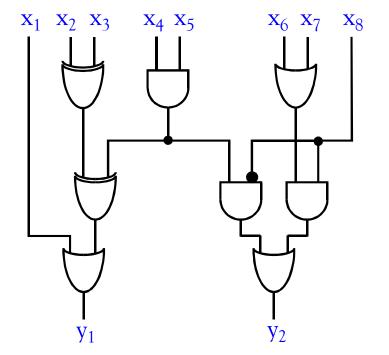

#### Example: Cost and depth of circuits

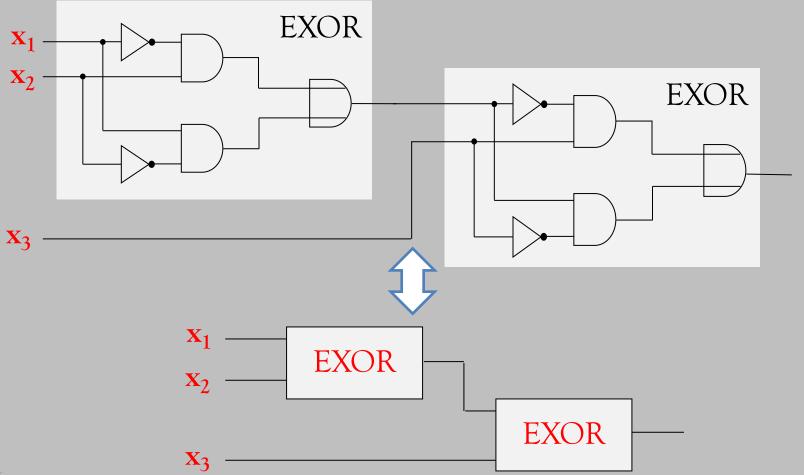

#### Hierarchical circuits

In hierarchical circuits,

subcircuits are represented by symbols.

The corresponding ("flat") circuit is obtained by replacing the symbols by their defining subcircuits.

#### Example Hierarchical circuits

#### Circuits vs Boolean functions

Every circuit computes a Boolean function.

But can **every** Boolean function be computed by a circuit?

#### Circuits vs Boolean functions

Theorem: Let  $f \in B_{n,m}$ . Then there is a circuit that computes f.

Reminder:

Lemma:

For every Boolean function  $f \in B_{n,1}$  there is a Boolean expression that describes f.

#### Circuits vs Boolean expressions

Lemma:

For every Boolean expression  $e \in BE(X_n)$ there is a circuit  $C = (X_n, G, typ, IN, Y_m)$ , such that  $\psi(e) = f_C$ .

*Proof*: By induction over the structure of the Boolean expression.

#### Recapitulation: Boolean expressions

#### **Definition:**

The set  $BE(X_n)$  of fully parenthesized Boolean expressions over  $X_n$  is the smallest subset of  $A^*$ , inductively defined as follows:

- The elements 0 and 1 are Boolean expressions

- The variables  $x_1, ..., x_n$  are Boolean expressions

- Let g and h be Boolean expressions. Then so is their Disjunction (g + h), their Conjunction (g · h), and their Negation (~g).

#### Circuits vs Boolean functions

Theorem:

Let  $f \in B_{n,m}$ .

Then there is a circuit that computes **f**.

Proof:

Case 1:  $f \in B_n = B_{n,1}$ .  $\exists e \in BE(X_n)$ , that computes f.

The theorem then directly follows from the previous lemma.

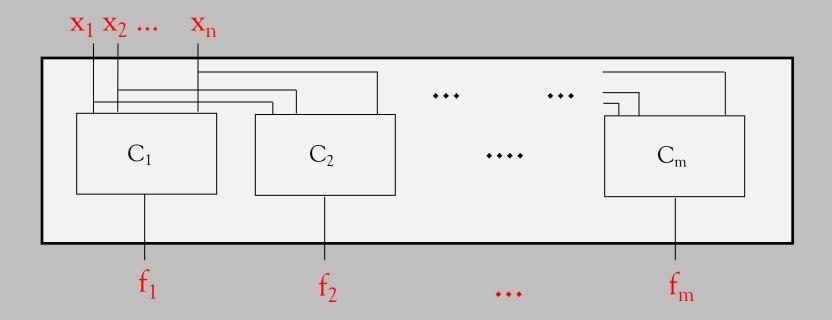

Case 2:  $f \in B_{n,m}$ ,  $m \ge 2$ . Interpret  $f : B_{n,m} = B^n \to B^m$  as a sequence of functions  $(f_1, ..., f_m)$  with  $f_i : B_n \to B$ .

Construct a circuit for each f<sub>i</sub>.

Compose the circuits (see the following illustration).

Circuits

# Construction of a circuit for a Boolean function from $B_{n,m}$ .

### Example: Generalized EXOR

#### Given:

Function

$$\operatorname{exor}_{16} \in \mathbf{B}_{16}$$

with

$\operatorname{exor}_{16}(x_1, \dots, x_{16}) = \left(\sum_{i=1}^{16} x_i\right) \mod 2 = 1$  if number of  $x_i$  with  $x_i = 1$  is odd

#### Wanted:

Circuit implementation for  $exor_{16}$ .

Assumption: exor<sub>2</sub> is an element of our cell library. Observations:

- 1.  $exor_{16}$  can be constructed from several  $\bigotimes = exor_2$ .

- 2.  $\otimes$  is an associative operation!

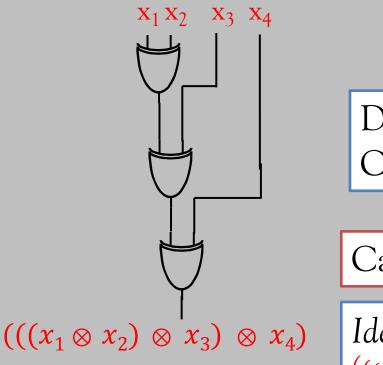

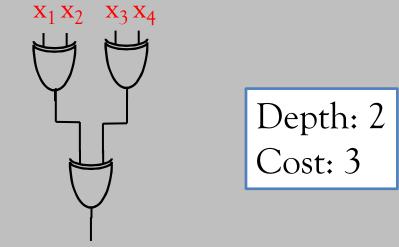

Implementation of exor<sub>4</sub>:

Can we do better?

*Idea*: Make use of associativity:  $((x_1 \otimes x_2) \otimes x_3) \otimes x_4) = ((x_1 \otimes x_2) \otimes (x_3 \otimes x_4))$

Better implementation of exor<sub>4</sub>:

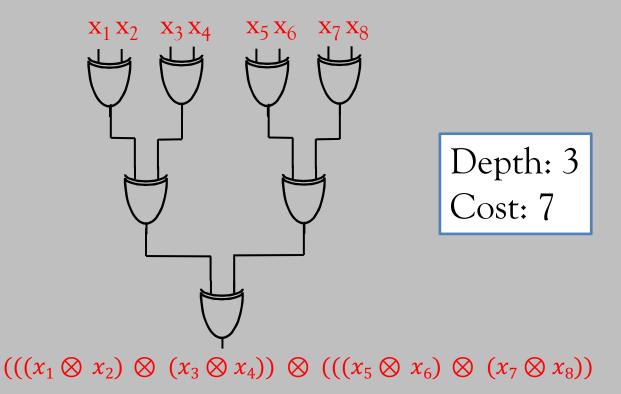

$((x_1 \otimes x_2) \otimes (x_3 \otimes x_4))$

Better implementation of exor<sub>8</sub>:

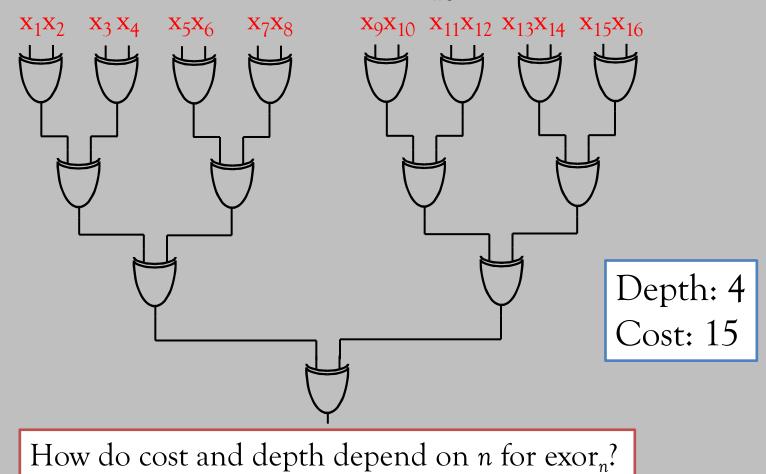

Better implementation of exor<sub>16</sub>:

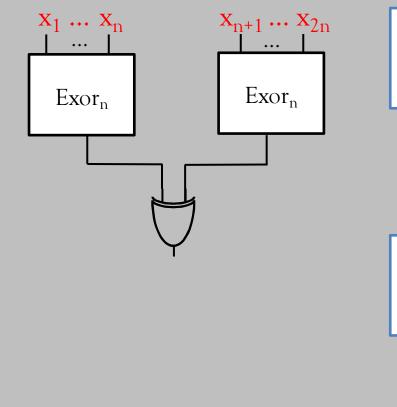

# Recursive construction of generalized EXOR

#### Implementation of exor<sub>2n</sub>:

$$depth(exor_{2n}) = depth(exor_{n})+1$$

$$depth(exor_{1}) = 0$$

$$\rightarrow$$

depth(exor<sub>n</sub>) = log<sub>2</sub> n

$$C(exor_{2n}) = 2 \cdot C(exor_n) + 1$$

$$C(exor_1) = 0$$

$$\rightarrow C(exor_n) = n-1$$

# Efficient implementation of **arbitrary** associative operations

Lemma:

The function  $x_1 \circ x_2 \dots \circ x_n$  can be implemented using  $\circ$  gates with 2 inputs in a circuit of depth  $\lfloor \log_2 n \rfloor$ .

Proof by induction over **n**.

## Two-level normal form of $EXOR_{16}$

*Question:* How large is the smallest Boolean polynomial of  $exor_{16}$ ?

Answer: 2<sup>15</sup> monomials with 16 literals each!

Question: How large it the smallest Boolean polynomial for  $exor_n$ ?

Answer:  $2^{n-1}$  monomials with *n* literals each!

Exponentially higher cost than the multi-level implementation!

Cost of the implementation of Boolean expressions via circuits

Define the cost C(E) of a Boolean expression E to be the number of operations in the expression.

Theorem:

For every Boolean expression  $e \in BE(X_n)$ there is a circuit  $C = (X_n, G, typ, IN, Y_m)$ , such that  $\psi(e) = f_C$  and  $C(C) \leq C(E)$ .

Follows from proof of earlier lemma.

Reusing subcircuits can sometimes help reduce the cost.

#### Cost of the implementation of Boolean functions via circuits

Theorem:

For every  $f \in \mathbf{B}_n$  there is a circuit C implementing f, s.t.  $C(C) \le n2^{n+1}$ -1 and depth(C)  $\le n+\lfloor \log_2 n \rfloor+1$ .

#### Proof sketch:

(Cost:) A function  $f \in B_n$  has at most  $2^n$  minterms. Every minterm can be implemented using 2n-1 gates. The disjunction of all minterms can be implemented using at most  $2^n$ -1 gates.

(Depth:) Every minterm can be implemented in depth  $\lceil \log_2 n \rceil + 1$ . The disjunction can be implemented in depth n (=  $\log_2 2^n$ ).

Circuits *implement* arbitrary Boolean functions from  $B_{n,m}$ .

Optimal Boolean polynomials can be much larger than corresponding multi-level circuits: **exponential differences** are possible!

#### Outlook

## There are **algorithms** to compute **optimal multi-level circuits**

- harder than computing minimal polynomials

- mostly heuristics, i.e., not guaranteed to be optimal

- not covered in this course

- *Here*: Circuits for special functions, in particular arithmetic